Описание

FPGA JTAG Open3S500E Стандартный # XC3S500E Spartan-3E ппвм Xilinx оценки макетная плата + XC3S500E Основной комплект

Обзор

Open3S500EЭто Плата развития FPGA, которая состоит из материнской платыDVK600И основная плата FPGACore3S500E.

Open3S500E поддерживает дальнейшее расширение с различными отдельно приобретаемый аксессуар доски для специфического применения. Модульная и открытая конструкция делает его идеальным для запуска разработки приложений с XILINX Spartan-3E series FPGA устройствами.

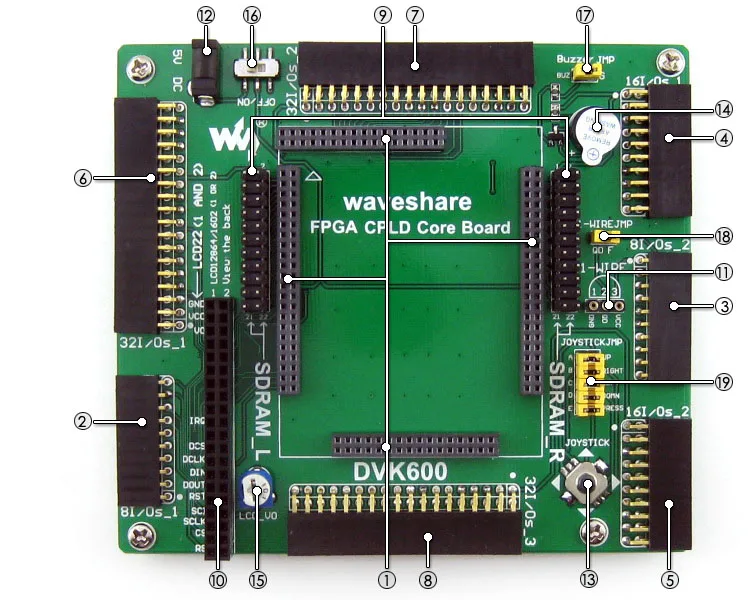

Что на материнской доске

FPGA CPLD разъем основной платы:Для легкого подключения картон для изготовления гильз, который интегрирует чип FPGA CPLD на бортовой Интерфейс 8I/Os_1,Для соединительных досок/модулей Интерфейс 8I/Os_2,Для соединительных досок/модулей Интерфейс 16I/Os_1,Для соединительных досок/модулей Интерфейс 16I/Os_2,Для соединительных досок/модулей 32I/Os_1 интерфейс,Для соединительных досок/модулей 32I/Os_2 интерфейс,Для соединительных досок/модулей 32I/Os_3 интерфейс,Для соединительных досок/модулей

FPGA CPLD разъем основной платы:Для легкого подключения картон для изготовления гильз, который интегрирует чип FPGA CPLD на бортовой Интерфейс 8I/Os_1,Для соединительных досок/модулей Интерфейс 8I/Os_2,Для соединительных досок/модулей Интерфейс 16I/Os_1,Для соединительных досок/модулей Интерфейс 16I/Os_2,Для соединительных досок/модулей 32I/Os_1 интерфейс,Для соединительных досок/модулей 32I/Os_2 интерфейс,Для соединительных досок/модулей 32I/Os_3 интерфейс,Для соединительных досок/модулейВсе интерфейсы ввода/вывода выше:

Может быть имитация как USART, I2C, SPI, PS/2, и т. д. Возможность вождения устройств, таких как FRAM, FLASH, USB, Ethernet и т. д.Для Джемперы 17-19:

Короткий Джемпер для подключения к I/Os, используемому в коде примера Откройте перемычку для подключения к другим разъемы в ассортименте с помощью перемычекDVK600 поддерживает широкий спектр различных картон для изготовления гильз, поэтому некоторые интерфейсы могут быть не подключены и бесполезны при подключении к определенной основной плате. Например, при подключении к Core3S500E/CoreEP2C8, глюкозы в крови тест 32I/Os_3 '-это не подключен.

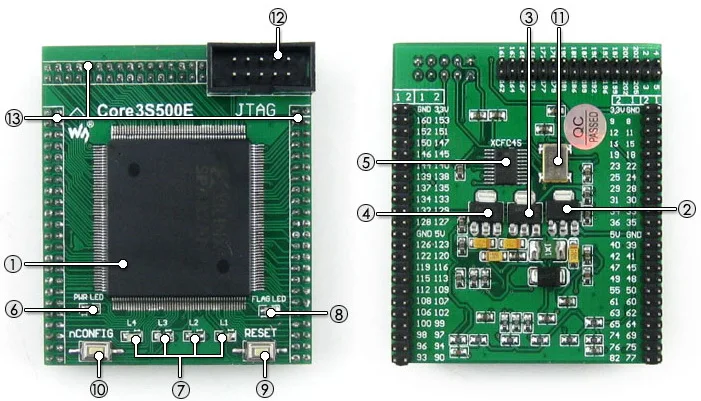

What's на Core3S500E

XC3S500E:XILINX Spartan-3E FPGA устройство, которое имеет: Рабочая частота:50 МГц Операционной Напряжение:1,15 ~ 3,3 В Посылка:QFP208 Ввода/вывода:116 LEs:500 K Оперативная память:360kb DCMs: 4 Отладки/программирования:Поддержка JTAG AMS1117-3.3,3,3 V регулятор напряжения AMS1117-2.5,2,5 V регулятор напряжения AMS1117-1.2,1,2 V регулятор напряжения XCF04S,Встроенная последовательная флэш-память, для хранения кода Мощность индикатор Светодиоды FPGA инициализации индикатора Кнопка сброса Nconfig кнопки:Для повторной настройки чипа FPGA, эквивалент переустановки мощности 50 м активный кварцевый генератор Интерфейс JTAG:Для отладки/программирования FPGA булавки расширитель,VCC, GND и все порты ввода/вывода доступны на дополнительные разъемы для дальнейшего расширения

XC3S500E:XILINX Spartan-3E FPGA устройство, которое имеет: Рабочая частота:50 МГц Операционной Напряжение:1,15 ~ 3,3 В Посылка:QFP208 Ввода/вывода:116 LEs:500 K Оперативная память:360kb DCMs: 4 Отладки/программирования:Поддержка JTAG AMS1117-3.3,3,3 V регулятор напряжения AMS1117-2.5,2,5 V регулятор напряжения AMS1117-1.2,1,2 V регулятор напряжения XCF04S,Встроенная последовательная флэш-память, для хранения кода Мощность индикатор Светодиоды FPGA инициализации индикатора Кнопка сброса Nconfig кнопки:Для повторной настройки чипа FPGA, эквивалент переустановки мощности 50 м активный кварцевый генератор Интерфейс JTAG:Для отладки/программирования FPGA булавки расширитель,VCC, GND и все порты ввода/вывода доступны на дополнительные разъемы для дальнейшего расширенияФото

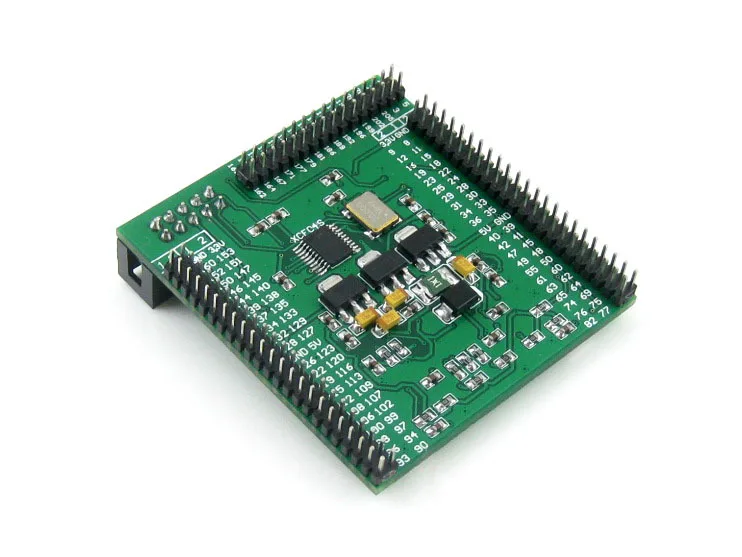

Open3S500E макетная плата

Open3S500E макетная плата

Open3S500E макетная плата (вид сзади)

Материнская плата печатная плата для DVK600

FPGA основной плате Core3S500E

FPGA основной плате Core3S500E

Подключение к различные периферийные устройства

Подключение к LCD12864

Подключение к LCD1602

Подключение к RS232 доска

Подключение к USB плата UART

Подключение к 8 сегментный светодиодный плате

Подключение к 8 кнопочным кнопкам

Подключение к 4x4 клавиатуры

Подключение к плата eeprom

Несколько периферийных устройств, подключенных к одному интерфейсу

Подключение к плата DataFlash

Подключение к CY7C68013A USB доска

Подключение к VGA PS2 доска

Подключение к любой вспомогательной плате, которая вам нужна

Примечание:

В Open3S500E не интегрировать любые программирования/функции отладки, программист/отладчик не требуется.

Аксессуары для плат на фото не включены в стоимость Open3S500E Стандартный посылка.

Примеры

В Open3S500E FPGA развитию поставляется с различными примеры болты с шестигранной головкой поддерживаемых периферийных устройств, которые дают вам быстрый старт для Развивайте свое собственное приложение.

| Периферийное устройство | Описание продукта: | Интерфейс | Verilog | VHDL |

|---|---|---|---|---|

| AT24CXX | EEPROM | I2C | Y | Y |

| FM24CXX | Фрам | I2C | Y | Y |

| AT45DBXX | DATAFLASH | SPI | Y | |

| PCF8563 | РТК | I2C | Y | |

| PCF8591 | 4xAD, 1xDA | I2C | Y | |

| DS18B20 | Температура датчик | 1-проводной | Y | |

| SP3232 | Последовательной связи | UART | Y | Y |

| SP3485 | Последовательной связи | UART | Y | Y |

| PL2303 | USB UART | UART | Y | Y |

| CY7C68013A | USB устройство | Ввода/вывода | Y | |

| Зуммер | Звуковое устройство | 1I/O (PWM) | Y | Y |

| PS/2 клавиатуры | Вход устройства | PS/2 | Y | Y |

| Одной кнопки | Вход устройства | ---- | Y | Y |

| 4x4 клавиатуры | Вход устройства | 8I/Os | Y | Y |

| Джойстик | Вход устройства | 5I/Os | Y | Y |

| Светодиодный | Дисплей устройства | ---- | Y | Y |

| 8 сегментный светодиодный | Дисплей устройства | 13I/Os | Y | Y |

| Монитор с видеографической матрицей | Дисплей устройства | VGA | Y | Y |

| Персонаж ЖК-дисплей | Дисплей устройства | 11I/Os | Y | Y |

| Графический ЖК-дисплей | Дисплей устройства | 11I/Os | Y | Y |

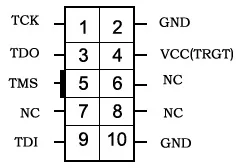

Отладки/программирования Интерфейс

В Open3S500E FPGA развитию интегрирует интерфейс JTAG для программирования/отладки.

Развития ресурсы

В Open3S500E FPGA развитию включает в себя руководство пользователя CD, включая следующие ресурсы развития, перечисленные ниже:

Сопутствующее программное обеспечение (Xilinx ISE 12-Поддерживает Winxp/Win7, не поддерживает Win8) Код демонстрационной версии (Verilog, VHDL) Схема (PDF) FPGA документация развитияПосылка содержит

Клиенты, которые купили этот товар, также купили

Характеристики

- Тип демоплаты

- Рука

- Номер модели

- Open3S500E Standard

- Бренд

- Waveshare

- Model Name

- Open3S500E Standard

- Debugging/Programming

- supports JTAG

- Open3S500E

- an FPGA development board

- XC3S500E

- the XILINX Spartan-3E FPGA device

- FPGA pins expander

- VCC, GND and all the I/O ports

- JTAG interface

- for debugging/programming

- I/Os

- 116

- Package

- QFP208

- Operating Frequency

- 50MHz

- Operating Voltage

- 1.15V~3.3V

- Demo Board Type

- Others